Electronic Science and Technology ›› 2023, Vol. 36 ›› Issue (9): 66-72.doi: 10.16180/j.cnki.issn1007-7820.2023.09.010

Previous Articles Next Articles

CHENG Tiantian,SONG Yukun

Received:2022-05-06

Online:2023-09-15

Published:2023-09-18

Supported by:CLC Number:

CHENG Tiantian,SONG Yukun. Optimization and Implementation of 2-Base Exponential Function Algorithm Based on FPGA[J].Electronic Science and Technology, 2023, 36(9): 66-72.

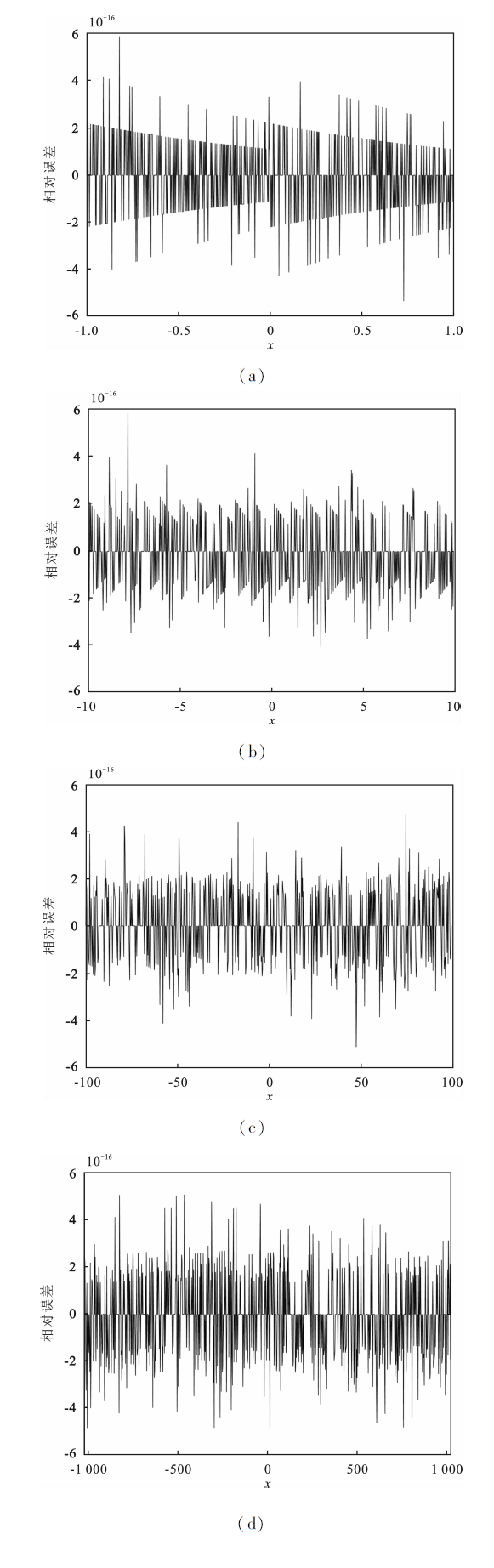

Table 3.

Calculation errors of circuits in different definition domains"

| 取值范围 | 平均相对误差 | 最大相对误差 | 均方误差 |

|---|---|---|---|

| [-1,1] | 7.554 2×10-18 | 3.638 4×10-16 | 1.331 4×10-16 |

| [-10,10] | 8.098 9×10-19 | 4.504 7×10-16 | 1.334 1×10-16 |

| [-100,100] | 6.220 8×10-18 | 4.533 4×10-16 | 1.337 3×10-16 |

| [-1 023,1 023] | 3.735 4×10-18 | 4.498 7×10-16 | 1.342 2×10-16 |

Figure 7.

Relative error of exponential function in different range (a)Relative error of exponential function in the range [-1,1] (b)Relative error of exponential function in the range [-10,10] (c)Relative error of exponential function in the range [-100,100] (d)Relative error of exponential function in the range [-1 023,1 023]"

| [1] | 张榜. X-DSP IP核Power函数部件的设计与验证[D]. 长沙: 国防科技大学, 2017:1-4. |

| Zhang Bang. Design and validation of the components of power function in IP core of X-DSP[D]. Changsha: National University of Defense Technology, 2017:1-4. | |

| [2] | 张俊. 高精度浮点指数和对数函数硬件设计[D]. 深圳: 哈尔滨工业大学, 2018:1-4,45-47. |

| Zhang Jun. High precision floating point exponent and logarithmic function haradware design[D]. Shenzhen: Harbin Institute of Technology, 2018:1-4,45-47. | |

| [3] | 史雄伟, 王成, 张春雷, 等. 基于 FPGA 的浮点指数函数算法研究与实现[J]. 计算机测量与控制, 2017, 25(10): 221-223. |

| Shi Xiongwei, Wang Cheng, Zhang Chunlei, et al. Algor-ithm research and implementation of float point expontial function based on FPGA[J]. Computer Measurement and Control, 2017, 25(10):221-223. | |

| [4] | 王鸿闯, 胡晓辉, 李薇. 一种基于改进阈值函数Contourlet域的图像去噪算法[J]. 电子科技, 2019, 32(4):44-48. |

| Wang Hongchuang, Hu Xiaohui, Li Wei. An image denoising algorithm based on improved threshold function contourlet domain[J]. Electronic Science and Technology, 2019, 32(4):44-48. | |

| [5] | 耿昭谦, 朱虎明, 李旭明, 等. 基于高性能计算的雷达信号处理研究综述[J]. 电子科技, 2021, 34(9):1-6. |

| Geng Zhaoqian, Zhu Huming, Li Xuming, et al. A review:Radar signal processing based on high performance computing[J]. Electronic Science and Technology, 2021, 34(9):1-6. | |

| [6] |

Pineiro J A, Ercegovac M D, Bruguera J D. Algorithm and architecture for logarithm,exponential and powering computation[J]. IEEE Transactions on Computers, 2004, 53(9):1085-1096.

doi: 10.1109/TC.2004.53 |

| [7] |

Piso D, Piñeiro J A, Bruguera J D. Analysis of the impact of different methods for division/square root computation in the performance of a superscalar micro processor[J]. Journal of Systems Architecture, 2003, 49(12-15):543-555.

doi: 10.1016/S1383-7621(03)00100-0 |

| [8] |

Pineiro J A, Bruguera J D. High-speed double-precision computation of reciprocal, division,square root and inverse square root[J]. IEEE Transactions on Computers, 2002, 51(12):1377-1388.

doi: 10.1109/TC.2002.1146704 |

| [9] | 潘宏亮. 浮点指数类超越函数的运算算法研究与硬件实现[D]. 西安: 西北工业大学, 2006:3-5. |

| Pan Hongliang. Research on algorithms and hardware implementation of floating-point exponential class transcendent functions[D]. Xi'an: Northwestern Polytechnical University, 2006:3-5. | |

| [10] |

Montuschi P, BrugueraJ D, Ciminiera L, et al. A digit- by-digit algorithm for mth root extraction[J]. IEEE Transactions on Computers, 2007, 56(12):1696-1706.

doi: 10.1109/TC.2007.70764 |

| [11] | 邹霞枫. 128位浮点指数函数的硬件实现[D]. 深圳: 哈尔滨工业大学, 2019:3-6. |

| Zou Xiafeng. Hardware implementation of 128-bit floating point exponential function[D]. Shenzhen: Harbin Institute of Technology, 2019:3-6. | |

| [12] | 张俊涛, 王红仓. 基于 FPGA的CORDIC 算法通用 IP 核设计[J]. 微计算机信息, 2008, 24(21):238-240. |

| Zhang Juntao, Wang Hongcang. Implementation of general CORDIC IP core based on FPGA[J]. Microcomputer Information, 2008, 24(21):238-240. | |

| [13] | 赵海燕, 周晓方, 周电. 对数/指数算法的改进及其 VLSI 实现[J]. 计算机工程与应用, 2007, 43(7):104-107. |

| Zhao Haiyan, Zhou Xiaofang, Zhou Dian. Arithmetic re-search of logarithm and anti-logarithm converters and VLSI implementation[J]. Computer Engineering and Applications, 2007, 43(7):104-107. | |

| [14] | 王少军, 张启荣, 彭宇, 等. 超越函数 FPGA 计算的最佳等距分段线性逼近方法[J]. 仪器仪表学报, 2014, 35(6): 1209-1216. |

| Wang Shaojun, Zhang Qirong, Peng Yu, et al. Optimal equidistant piecewise linear approximation algorithm for the computation of transcendental functions in FPGA[J]. Chinese Journal of Scientific Instrument, 2014, 35(6):1209-1216. | |

| [15] |

Schulte M J, Swartzlander E E. Hardware designs for exactly rounded elementary functions[J]. IEEE Transactions on Computers, 1994, 43(8):964-973.

doi: 10.1109/12.295858 |

| [16] | 林凯文, 陈志坚, 刘东启. 基于泰勒展开的低成本e指数函数电路设计[J]. 计算机应用研究, 2018, 35(6):1761-1763,1782. |

| Lin Kaiwen, Chen Zhijian, Liu Dongqi. Design and optimization of exponential function based on Taylor expansion[J]. Application Research of Computers, 2018, 35(6):1761-1763,1782. | |

| [17] | 牟胜梅, 李兆刚. 一种面向FPGA的指/对数函数求值算法[J]. 计算机工程与应用, 2011, 47(33):59-61. |

| Mou Shengmei, Li Zhaogang. FPGA-oriented evaluation algorithm for exponential and logarithm functions[J]. Computer Engineering and Applications, 2011, 47(33):59-61. | |

| [18] |

Ypma T J. Historical development of the Newton-Raphson method[J]. SIAM Review, 1995, 37(4):531-551.

doi: 10.1137/1037125 |

| [1] | ZHANG Zhihao,FU Dongxiang,YAN Rui. A Measuring System for Frame Size Based on Image Processing Technology [J]. Electronic Science and Technology, 2022, 35(11): 42-47. |

| [2] | BI Zaorong, TONG Dongbing, CHEN Qiaoyu. Design of Speaker Recognition System Based on Fast MFCC Calculation [J]. , 2018, 31(4): 25-. |

| [3] | GONG Xiaoyan. Realization of Beam Control System of Small Phased Array Radar [J]. , 2015, 28(6): 155-. |

| [4] | GUI Tengye,CHEN Shuo,WEI Lizhi,CUI Zhijun,ZHOU Xiaolin. Prediction and Countermeasures of Infectious Diseases Based on ARIMA [J]. , 2015, 28(12): 48-. |

| [5] | SHAO Xiaopeng,JIN Zhenhua,WANG Yang. Improved Algorithm for Removing Stripe Noise of Infrared Images [J]. , 2013, 26(10): 83-. |

| [6] | CHEN Mi-Hui, HE Xiu-Kun, MA Nong-Nong, CAO Quan-Xi. SIMS Test of Phosphorus in Silicon Wafer [J]. , 2010, 23(9): 68-. |

|